### EPM7032SLI44-7

Data Sheet

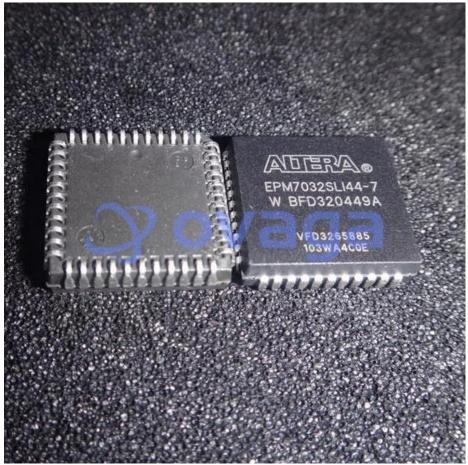

#### CPLD MAX? 7000S Family 600 Gates 32 Macro Cells 116.3MHz 5V 44-Pin PLCC Tube

| Manufacturers | Altera Corporation (Intel) |

|---------------|----------------------------|

| Package/Case  | PLCC44                     |

| Product Type  | Programmable Logic ICs     |

| RoHS          |                            |

| Lifecycle     |                            |

Images are for reference only

Application

| Please submit RFQ for EPM7032SLI44-7 | r Email to us: sales@ovaga.com We will contact you in 12 hour | s. <u>RFQ</u> |

|--------------------------------------|---------------------------------------------------------------|---------------|

|--------------------------------------|---------------------------------------------------------------|---------------|

### **General Description**

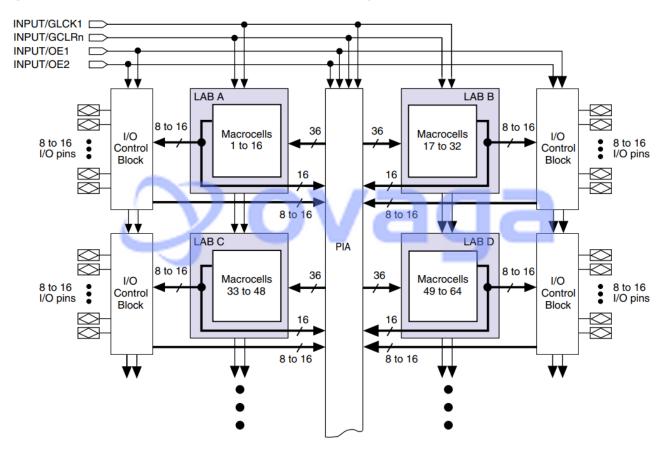

EPM7032SLI44-7 is a specific type of programmable logic device (PLD) manufactured by Intel (previously known as Altera). It is a member of the MAX 7000 series of PLDs and features 32 macrocells, which can be used to implement logic functions, arithmetic operations, and state machines.

### Features

|                                                                                                            | 11                              |

|------------------------------------------------------------------------------------------------------------|---------------------------------|

| 32 macrocells with 32 product terms each                                                                   | Logic control and sequencing    |

| 32 input pins and 32 output pins                                                                           | Data encryption and decryption  |

| Operating voltage range of 4.75V to 5.25V                                                                  | Data compression and            |

| Low-power standby mode with less than $10\mu A$ typical current consumption                                | decompression                   |

| In-system programmable through the Joint Test Action Group (JTAG) interface                                | Address decoding and routing    |

| High-reliability, non-volatile design with no requirement for external programming voltage or power supply | Signal processing and filtering |

| during programming                                                                                         | Motor control and power         |

|                                                                                                            | management                      |

Figure 1. EPM7032, EPM7064 & EPM7096 Device Block Diagram

Dalatad Duaduata

**Ovaga Technologies Limited**

### **EP4CE55F29C8N**

Altera Corporation (Intel) FBGA-780

## Altera Corporation (Intel) TQFP-144

# <u>EP2C35F672C8N</u>

Altera Corporation (Intel) FBGA-672

Altera Corporation (Intel) FBGA-484

### EPM240M100C5N

Altera Corporation (Intel) BGA-100

### EPM570F256C5N

Altera Corporation (Intel) FBGA-256

### **EPM7128AETC100-10**

Altera Corporation (Intel) TQFP-100

### EP2C35F484I8N

Altera Corporation (Intel) FBGA-484